Why SiC Needs a Stronger European Materials Backbone

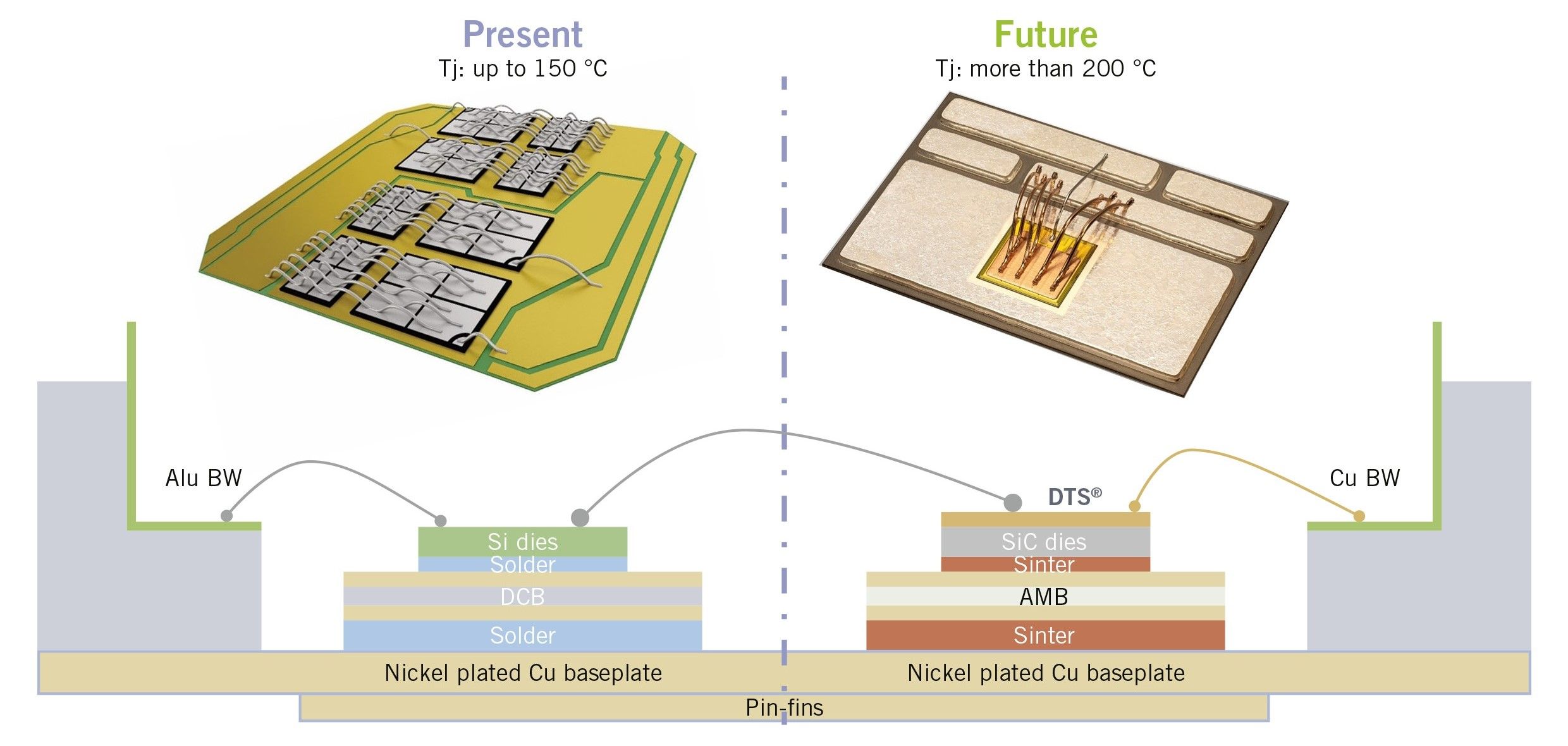

Across mobility, renewable energy, and power infrastructure, the shift toward higher‑efficiency and lower‑emissions technologies is accelerating. In this evolving landscape, Silicon Carbide (SiC) has become a key enabler of high‑temperature, high‑frequency, and high‑power‑density systems. But unlocking SiC’s full performance is not only a matter of advanced device engineering it depends equally on the materials, substrates, and interconnects that form the structural backbone of every module.

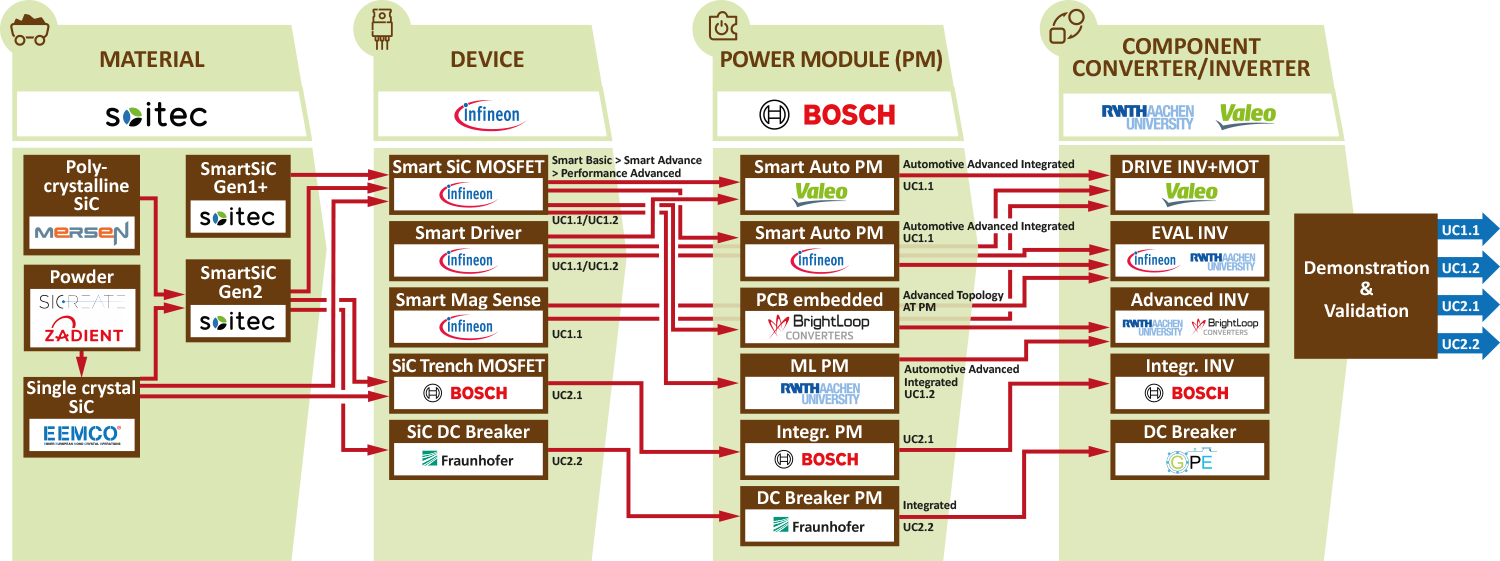

Enter FastLane, a European initiative launched in 2024 and built around a simple but ambitious mission: strengthen the EU’s independence, sustainability, and competitiveness in SiC power electronics from raw materials to system‑level demonstrators.

The project unites 29 partners from seven countries, blending research institutes, SMEs, and industry leaders to accelerate innovation across the SiC value chain. Under this framework, Heraeus Electronics contributes crucial packaging technologies that improve module performance, durability, and manufacturability.

Building a Scalable, Independent SiC Supply Chain

As demand surges for SiC‑based converters, traction inverters, and grid‑connected modules, Europe faces three structural challenges:

- Dependence on non‑EU raw materials

- Limited regional manufacturing capacity for advanced substrates and packaging materials

- Pressure to reduce environmental impact across the product lifecycle

FastLane addresses these issues head‑on with a coordinated multi‑year program focused on:

- Establishing independent SiC materials and device supply chains

- Developing packaging technologies that enable higher efficiency and lower CO₂ per module

- Creating system‑level demonstrators for mobility and energy sectors

Heraeus Electronics’ contributions target the packaging stage — the point where material science and system engineering meet.

Three Packaging Materials Innovations Accelerating SiC Integration

1. Silver Sintering for High‑Performance, Low‑Cost AMB Attachment:

1. Silver Sintering for High‑Performance, Low‑Cost AMB Attachment:

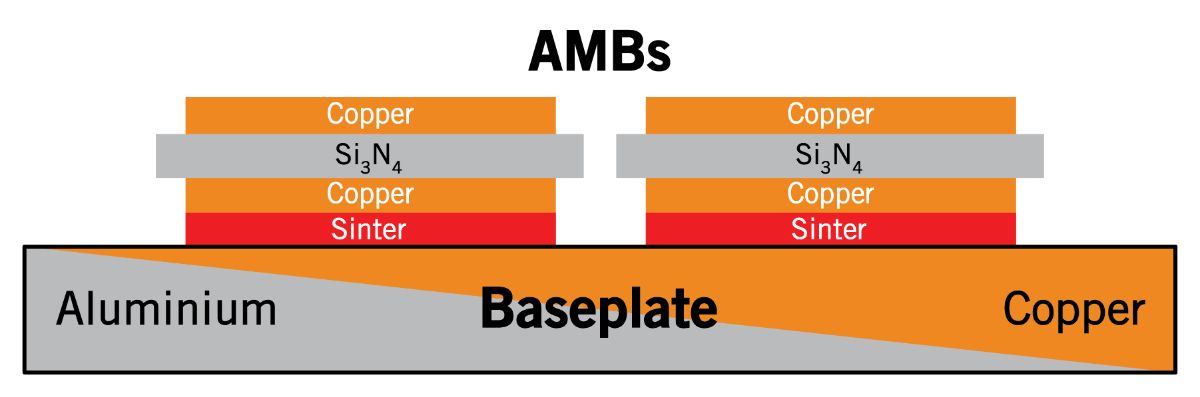

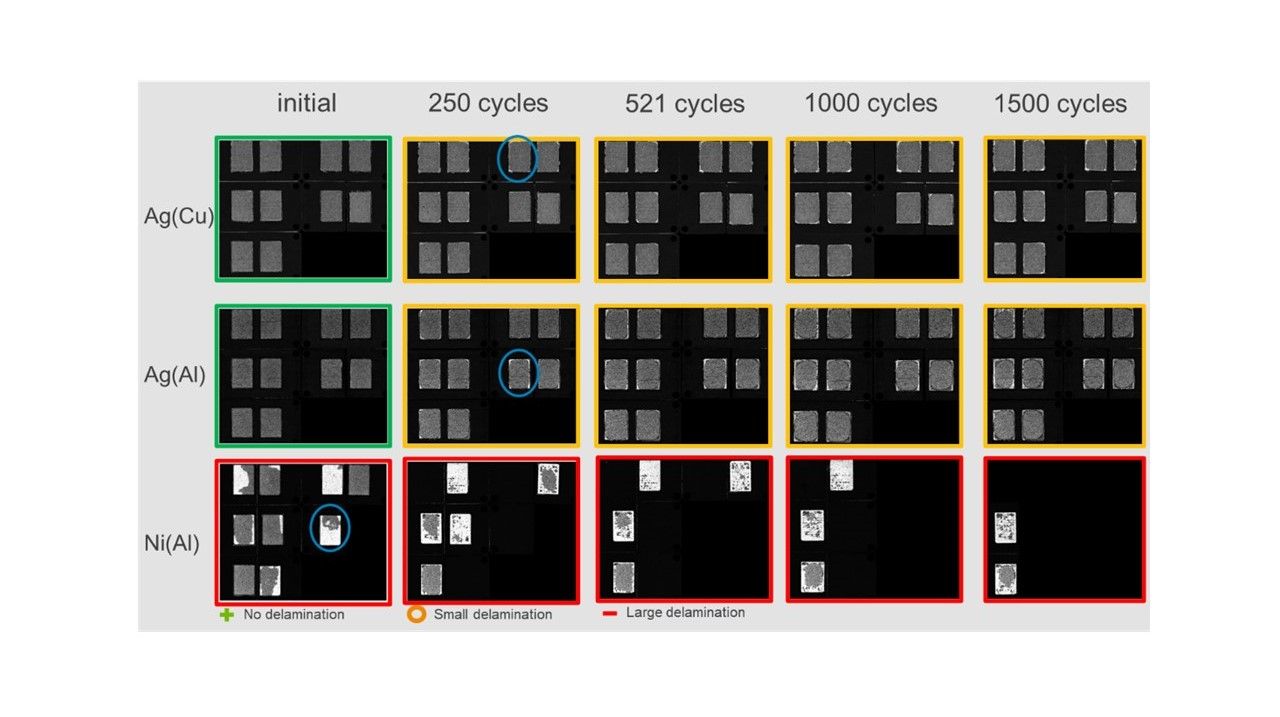

Traditional SiC power module architectures often rely on copper baseplates with precious‑metal metallization, which adds weight, cost, and supply risk. Heraeus Electronics addresses these limitations through a specialized silver sinter paste (PE 360P) that enables the attachment of Active Metal Brazed (AMB) substrates not only on copper but also to aluminum baseplates

Why this matters

- Up to 70% weight reduction compared to copper

- Cost savings up to 91%, making SiC modules more competitive in high‑volume markets

- Strong adhesion, demonstrated by <5% delamination after 1,500 temperature cycles

Reliable performance, even with coated aluminum vs. copper baseplates

These results show that sintered silver module attach on aluminum creates a lighter, more economical foundation for next‑generation SiC power modules without sacrificing reliability. Ongoing project work continues to optimize sintering directly on non‑precious‑metal coatings, i.e. copper to simplify the production flow further.

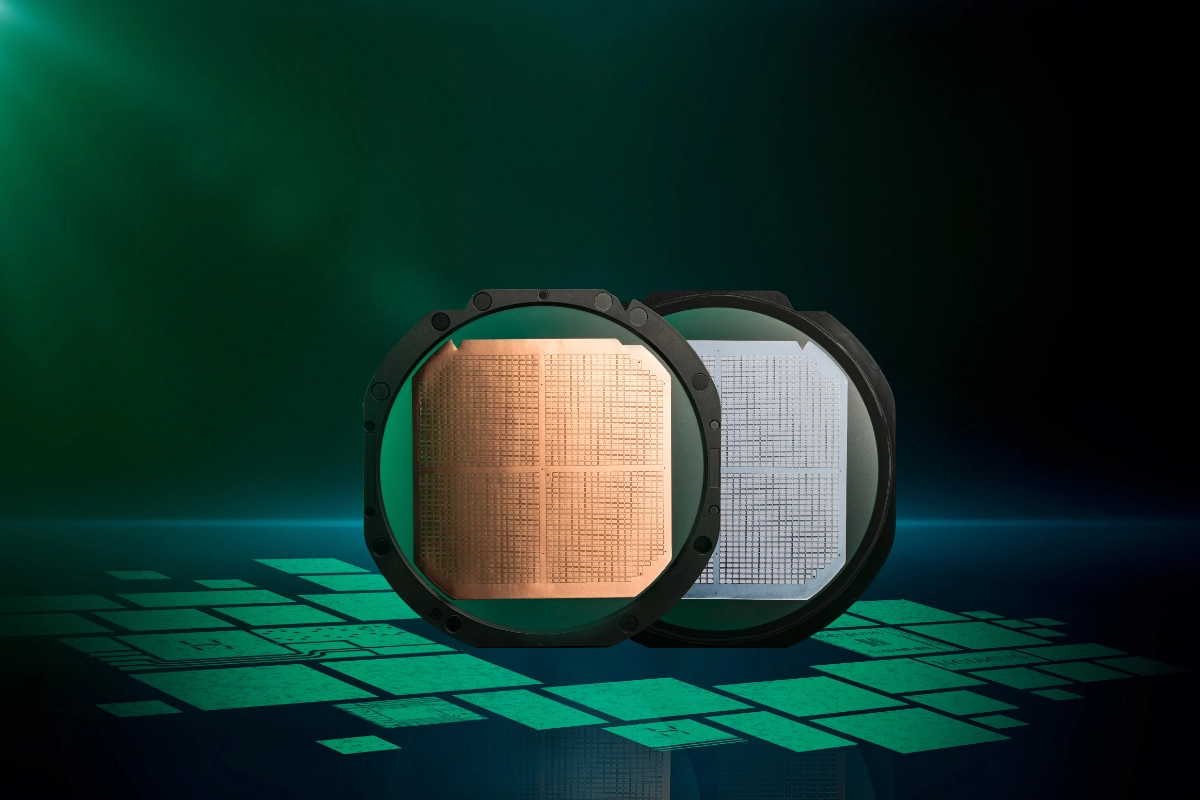

2. Silver‑Free, Low‑Inductance AMB Substrates Using Si₃N₄ Ceramics:

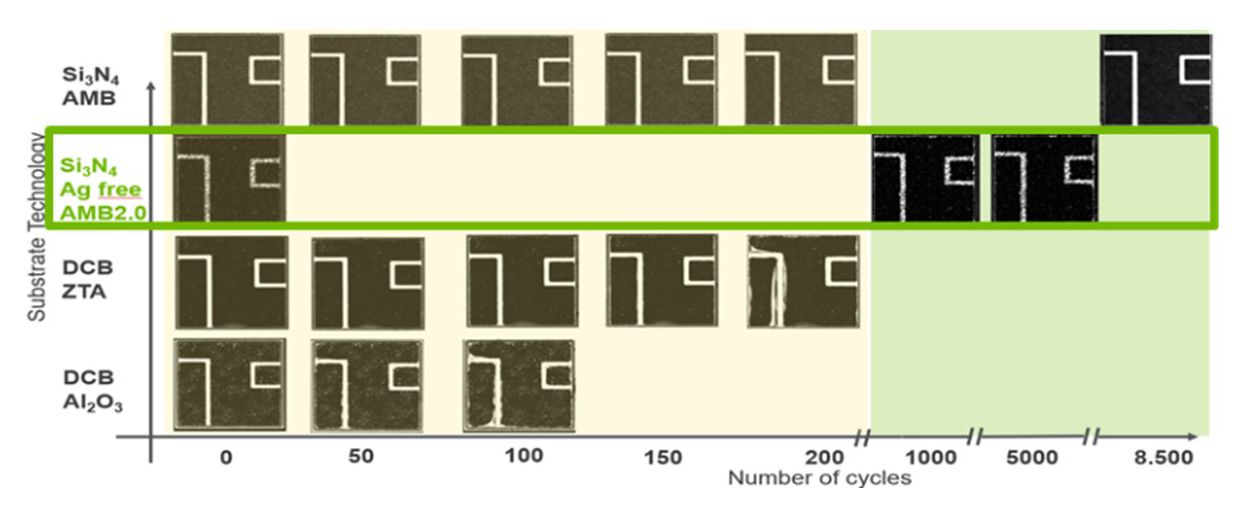

A major bottleneck in high‑frequency SiC modules is parasitic inductance, which causes voltage overshoot, switching losses, and EMI challenges. To address this, Heraeus Electronics developed silver‑free AMB substrates using silicon nitride ceramic (Si₃N₄).

Key benefits

- Elimination of high silver content, reducing cost and avoiding Ag‑migration reliability issues

- Lower inductance layouts, enabling cleaner SiC switching

- Improved thermal shock resilience (–65 °C to +150 °C)

- Performance surpassing conventional DCB substrates, and matching Ag‑containing AMB

- Strengthened European supply chain, with all key manufacturing steps located in Europe

The adoption of these new AMB substrates provides a foundation for low‑inductance, high‑current designs suited for both traction inverters and stationary energy systems. Their integration into Valeo’s low‑inductance module designs is already planned as a next step within FastLane.

3. Die Top System (DTS®): Enabling Highly Reliable Copper Wire Bonding

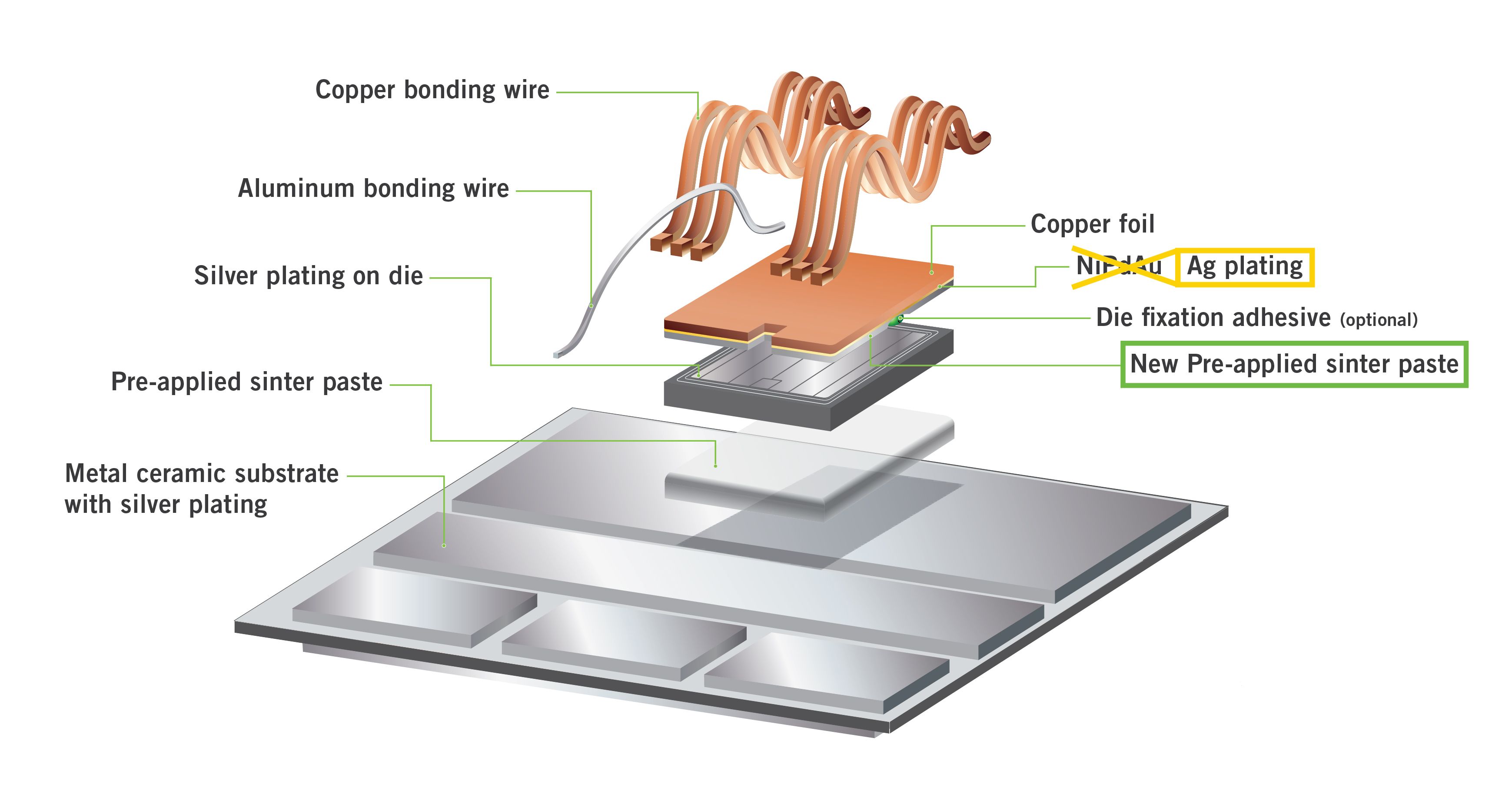

Top‑side interconnects exert significant influence over module durability — especially under high‑temperature and high‑current operation. Heraeus Electronics developed the Die Top System (DTS®) to enable copper wire bonding directly onto SiC dies.

What DTS® delivers

- A copper foil with pre‑applied sinter material that forms a robust bonding interface

- More than 10× reliability improvement over aluminum wire bonding

- The DTS® Silver variant replaces NiPdAu with Ag plating for simpler sintering

- Future developments include laser‑structured DTS® Silver, achieving bonding geometries as small as 0.5 × 0.5 mm²

Copper wire bonding is crucial for high‑current SiC modules, making DTS® a critical enabler of next‑generation inverter topologies in both automotive and industrial applications.

First‑Year Achievements: Progress from Concept to Integration:

During the first year of FastLane, Heraeus Electronics and its partners successfully delivered three packaging building blocks now moving into module‑level integration and reliability testing:

- Silver sinter paste optimized for AMB‑to‑aluminum baseplate attachment

- Silver‑free Si₃N₄ AMB substrates that reduce cost and inductance

- Copper‑bonded die‑top systems for high‑reliability SiC dies

These innovations are now being validated across multiple SiC power module architectures to assess switching behavior, mechanical stability, and long‑term endurance under representative operating conditions.

Real‑World Demonstrators: Mobility and Energy Systems

FastLane links material innovations to system‑level use cases in two high‑impact sectors: automotive and energy.

E‑Mobility Demonstrators:

- Light commercial vehicles (UCs 1.1 & 1.2a): Targeting scalable inverter platforms for mainstream production

- Ultra‑class haul trucks (UC 1.2b): Stress‑testing SiC modules under extreme loads, vibration, and heat

These demonstrators help validate module designs where weight reduction, thermal resistance, and interconnect robustness directly influence performance and service life.

Energy System Demonstrators:

- Power inverters for electrolyzers (UC 2.1): Supporting the growing role of hydrogen in Europe’s energy transition

- Solid‑state circuit breakers (UC 2.2): Improving grid protection and enabling advanced battery storage systems

Each demonstrator creates a feedback loop between material performance and system‑level requirements, accelerating application‑ready SiC module development.

Conclusion: A Stronger, More Resilient European SiC Ecosystem

FastLane’s packaging contributions are more than incremental technical improvements - they represent strategic building blocks for Europe’s future in power electronics.

By combining:

- Silver sintering for light, cost‑effective substrate attach

- Silver‑free, low‑inductance AMB substrates on Si₃N₄

- Copper‑compatible DTS®

Europe moves closer to achieving:

- Higher efficiency in SiC power modules

- Lower CO₂ emissions across materials and manufacturing

- Reduced dependence on non‑EU raw materials

- A durable, strategically important SiC supply chain

These advancements set the foundation for high‑performance SiC demonstrators and, ultimately, accessible and reliable power solutions for mobility, renewable energy, and grid applications throughout Europe.

ACKNOWLEDGMENT

The project is supported by the Chips Joint Undertaking (JU) and its members, including top-up funding by Austria, France, Germany, Romania, Slovakia, under grant agreement No 101139788.

In Germany, this project is co-funded by the Federal Ministry of Research, Technology and Space (project no. 16MEE0415).